1. Des tubes à vide aux circuits intégrés

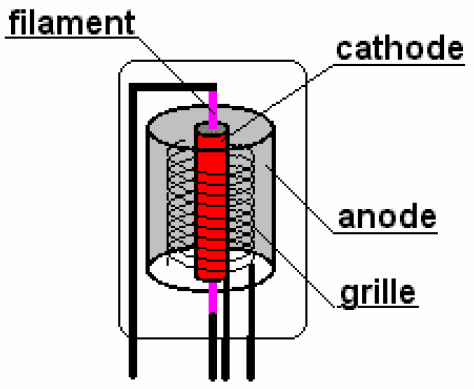

Les premiers calculateurs utilisaient des tubes à vide comme la triode, qui contrôle un flux d’électrons entre la cathode et l’anode grâce à une grille. Cette technologie a permis des avancées majeures, mais elle présentait de sérieux inconvénients : les machines étaient volumineuses, fragiles, très chaudes et extrêmement gourmandes en énergie. L’ENIAC, par exemple, comptait environ 17 500 tubes et occupait une salle entière.

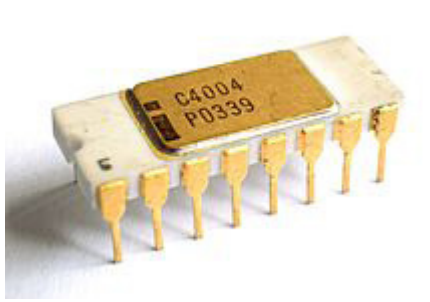

En 1947, Bardeen, Brattain et Shockley inventent le transistor, beaucoup plus petit et efficace. Dix ans plus tard, Kilby (TI) et Noyce (Fairchild) rassemblent plusieurs transistors sur une même puce : c’est la naissance du circuit intégré (CI).

2. Lire un schéma : blocs indispensables

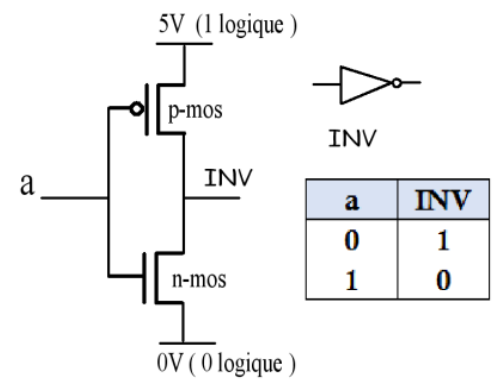

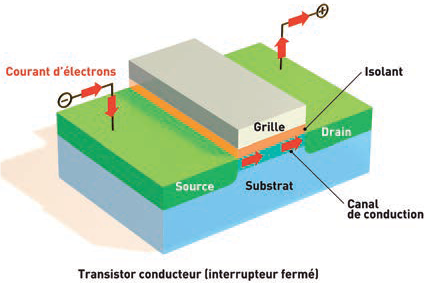

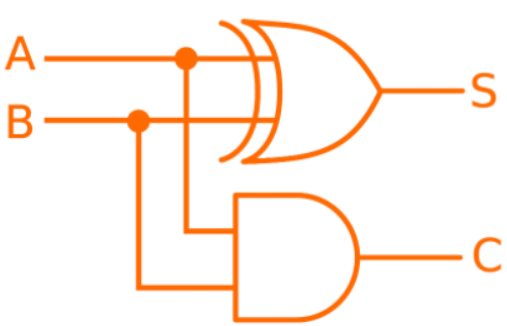

Un transistor MOS se comporte comme un interrupteur commandé : une tension appliquée sur la grille autorise ou bloque le passage du courant entre la source et le drain. Des millions de MOS assemblés forment des portes logiques (NOT, AND, OR, XOR), puis des blocs combinatoires tels qu’un additionneur, un multiplexeur ou un décodeur.

Lorsqu’on mémorise des bits au rythme d’une horloge, on obtient des blocs séquentiels : bascules, registres et compteurs. L’horloge (CLK) cadence la mise à jour de ces éléments à des instants précis (souvent au front montant). Les différents blocs communiquent via des bus de données, d’adresses et de contrôle, avec une alimentation (VDD) et une masse (GND).

Repères visuels utiles

Le rond sur la sortie d’une porte indique une inversion (NOT). Les symboles OR et XOR sont arrondis, l’AND est plus rectangulaire. Un petit triangle dessiné sur une entrée signale souvent la présence de l’horloge.

Sur les schémas, les bus sont parfois épaissis pour signifier plusieurs lignes en parallèle (par exemple un bus 8, 16 ou 32 bits).

Exemple : dans un additionneur complet (1 bit), la somme s’obtient grâce aux XOR tandis que la retenue (carry) résulte d’un assemblage de AND et de OR.

3. Pourquoi intégrer ? Vitesse et consommation

Intégrer les composants sur une même puce raccourcit drastiquement les trajets électriques et réduit les effets parasites. Les signaux se propagent plus vite, les pertes sont moindres et la consommation baisse. La fiabilité progresse aussi, car il y a moins de soudures et de liaisons susceptibles de défaillir. Enfin, la fabrication par “tranches” de silicium (wafer) permet d’atteindre des densités très élevées pour un coût unitaire réduit.

| Aspect | Montage discret | Intégration sur puce |

|---|---|---|

| Trajets électriques | Longs (fils/cartes) | Très courts : délais de propagation réduits |

| Parasites | Capacités et inductances élevées | Parasites atténués, pertes plus faibles |

| Consommation | Chauffe importante | Moindre grâce aux MOS et aux trajets courts |

| Fiabilité | Nombreuses liaisons | Moins de points de panne |

| Densité / coût | Faible / élevé | Très élevée / coût unitaire plus bas |

À retenir. En réduisant les distances et les parasites, un circuit intégré atteint des fréquences plus élevées à consommation égale, ou une consommation plus basse à performances comparables.

4. Miniaturisation, SoC, horloge et cœurs

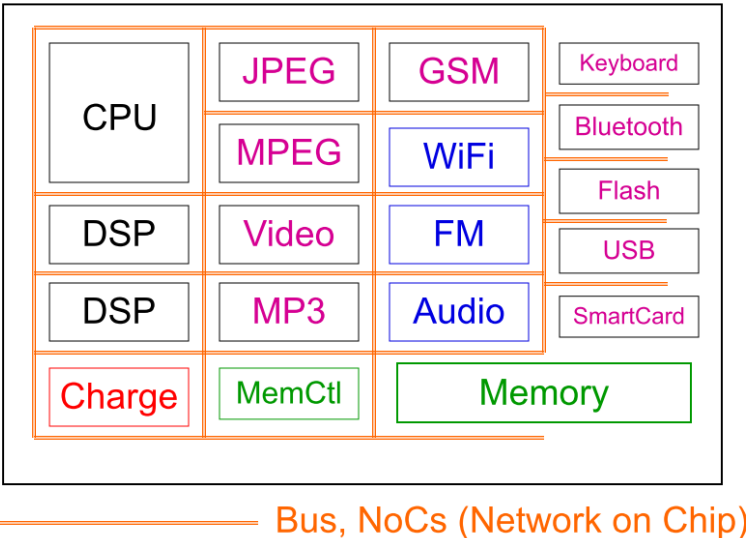

La loi de Moore a longtemps décrit le doublement régulier de la densité des transistors, ce qui a amélioré les performances et fait baisser les coûts. Aujourd’hui, l’intégration se poursuit à travers les SoC : une puce unique réunit l’unité centrale (CPU), le processeur graphique (GPU), des mémoires et de nombreux contrôleurs, ce qui augmente l’efficacité énergétique et la compacité, notamment sur mobile.

L’horloge détermine le rythme auquel les registres se mettent à jour. Augmenter sa fréquence accroît le débit théorique, mais provoque aussi une hausse de la consommation et de la chaleur. Pour continuer à accélérer, les concepteurs ajoutent des cœurs et exploitent le pipelining : plusieurs étapes d’instructions s’enchaînent en parallèle, ce qui augmente le débit sans nécessairement augmenter la fréquence.

5. Limites actuelles de la miniaturisation

Pour continuer à progresser malgré les limites physiques, l’industrie combine plusieurs approches :

- Empilement 3D : on empile plusieurs couches (ex. mémoire HBM au-dessus du processeur) pour raccourcir les trajets et augmenter le débit ; le défi, c’est la dissipation thermique.

- Chiplets : on assemble plusieurs petites puces (CPU, GPU, E/S…) sur un même support ; meilleur rendement, coûts réduits et liberté de mélanger des procédés de gravure différents.

- Spécialisation des puces : on ajoute des accélérateurs dédiés (GPU, NPU/TPU, encodeurs vidéo…) qui exécutent certaines tâches bien plus efficacement qu’un CPU généraliste.

Ouverture. Quand les transistors classiques approchent leurs limites physiques, une autre voie de calcul se dessine : l’informatique quantique, qui utilise des qubits capables de superposition et d’intrication.

6. Du design à la fabrication (silicium)

La fabrication d’une puce commence par la conception assistée par ordinateur : les blocs logiques sont décrits, simulés, puis placés et routés. Sur le silicium, des étapes répétées de dépôts, de photolithographie, de gravure, de dopage et de métallisation créent les transistors et leurs interconnexions sur plusieurs couches. Les circuits sont ensuite testés, découpés, encapsulés et qualifiés avant d’être livrés.

Pour une vue d’ensemble en vidéo, voir : Les 6 étapes clés.

Application : demi-additionneur (1 bit)

- En s’appuyant sur le schéma du demi-additionneur ci-dessous, expliquer le rôle des portes XOR et AND dans la formation de la somme S et de la retenue Cout.

- Comparer en deux phrases un montage discret de demi-additionneur et son équivalent en circuit intégré : que change l’intégration sur les trajets électriques, la vitesse et la consommation ?

- Un SoC de smartphone intègre CPU, GPU et mémoire proches : citer deux raisons précises expliquant pourquoi cela améliore l’autonomie.

| A | B | S | Cout |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |